Classification of ICs

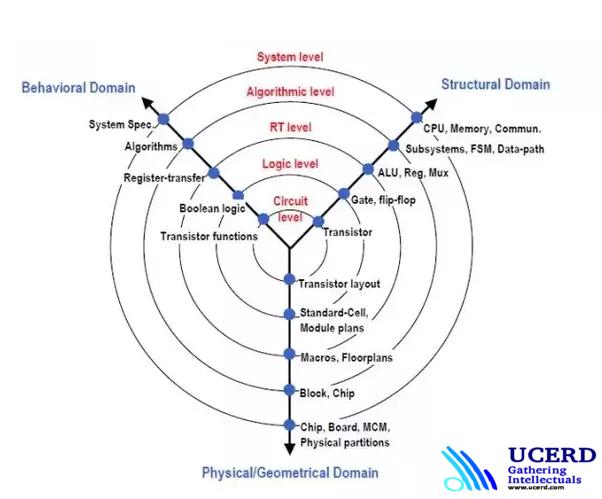

Design Flow (Y-Map)

Fabrication Process

VLSI Components and Architectures

MOS Transistor Theory

Types of Integrated Circuits

MOS, NMOS, PMOS, CMOS

Combinational Logic Circuits

Multiplexer, Encoder, Decoder, State Machine, Orbiter and Scheduler

Tools: ROCCC, C2HDL LEGUP, Vivado, Quartus, Modelsim

Components: ALU, Buses, Registers etc.

Using processors, caches, buses etc.

Multi Processor System Design

Gallium arsenide, Graphene etc.

Ultra-Fast VLSI Circuits and System and their Design

3D Fabrication

Ultra-Fast VLSI Circuits and System and their Design

3D FPGA i.e Tabaula etc

Analog Circuit Design (Field Programmable Analog Arrays) FPAA

Complex Engineering Problem

Graphene transistors

VLSI tool for graphene transistors

VLSI Processor Design

(List of Opensource Processors)

VLSI System on Chip Design

Graphene transistors

VLSI tool for graphene transistors

VLSI Processor Design

(List of Opensource Processors)

VLSI System on Chip Design

Book: CMOS VLSI Design_ A Circuits and Systems Perspective (4th Edition 2010)

FPAA

GaAs

A Practical Approach to VLSI System on Chip (SoC) Design. A Comprehensive Guide

VLSI Physical Design: From Graph Partitioning to Timing Closure

FPAA

GaAs

A Practical Approach to VLSI System on Chip (SoC) Design. A Comprehensive Guide

VLSI Physical Design: From Graph Partitioning to Timing Closure

Video Tutorials:

Cadence Virtuoso Schematic, Layout Design and Simulations: Modularity, Grid System and DRC (Youtube)

Digital Simulations (Youtube)

Cadence Virtuoso Schematic, Layout Design and Simulations: Modularity, Grid System and DRC (Youtube)

Digital Simulations (Youtube)

Dr. Tassadaq Hussain:

He is a permanent faculty member at, Riphah International University.

He did his Ph.D. from Barcelona-tech Spain, in collaboration with Barcelona Supercomputing Center and Microsoft Research Center.

He is a member of HiPEAC: European Network on High Performance and Embedded Architecture and Compilation, Barcelona Supercomputing Center and Microsoft ResearchCentre Spain.

Until January 2018, he had more than 14 years of industrial experience including, Barcelona Supercomputing Centre Spain, Infineon technology France, Microsoft Research Cambridge, PLDA Italia, IBM Zurich Switzerland, and REPSOL Spain. He has published more than 50 international publications and filed 5 patents.

Tassadaq's main research lines are Machine Learning, Parallel Programming, Heterogeneous Multi-core Architectures, Single board Computers, Embedded Computer Vision, Runtime Resource Aware Architectures, Software Defined Radio and Supercomputing for Artificial Intelligence and Scientific Computing.

www.tassadaq.ucerd.com

He is a permanent faculty member at, Riphah International University.

He did his Ph.D. from Barcelona-tech Spain, in collaboration with Barcelona Supercomputing Center and Microsoft Research Center.

He is a member of HiPEAC: European Network on High Performance and Embedded Architecture and Compilation, Barcelona Supercomputing Center and Microsoft ResearchCentre Spain.

Until January 2018, he had more than 14 years of industrial experience including, Barcelona Supercomputing Centre Spain, Infineon technology France, Microsoft Research Cambridge, PLDA Italia, IBM Zurich Switzerland, and REPSOL Spain. He has published more than 50 international publications and filed 5 patents.

Tassadaq's main research lines are Machine Learning, Parallel Programming, Heterogeneous Multi-core Architectures, Single board Computers, Embedded Computer Vision, Runtime Resource Aware Architectures, Software Defined Radio and Supercomputing for Artificial Intelligence and Scientific Computing.

www.tassadaq.ucerd.com

Very Large Scale integration (VLSI) Design

UCERD Rawalpindi

Supercomputing Center

UCERD Murree

VLSI Design course emphasizes on imparting overall exposure to the concept and design methodologies of all significant aspects of VLSI engineering relevant to the industry needs. The program offers in-depth, hands-on training on various design methods such as gate level, register transfer level, abstract level designs, etc. At the end of the course, the student can understand the VLSI manufacturing processor, solve a real-world problems and map and port these issues in an integrated circuit.

At the end of my course, students should learn:

To identify the Physical Layout and Gate Level System Design using 65 nm ASIC technology.

To discuss a scalar RISC core and Application-Specific Hardware Accelerators.

To design and program Uni-core System on Chip (SoC) and Multi-core (SoC) architectures. Bus System Performance (data rate), Processor Performance (FLOPS), Memory Read Write Time.

To use an FPGA logic block for gate and switch level systems.

To develop a layout of semi custom ASIC logic cell of three input lookup table (LUT), an FPGA Configurable Logic Block (CLB by using VLSI Digital Schematic Editor & Simulator.

At the end of my course, students should learn:

To identify the Physical Layout and Gate Level System Design using 65 nm ASIC technology.

To discuss a scalar RISC core and Application-Specific Hardware Accelerators.

To design and program Uni-core System on Chip (SoC) and Multi-core (SoC) architectures. Bus System Performance (data rate), Processor Performance (FLOPS), Memory Read Write Time.

To use an FPGA logic block for gate and switch level systems.

To develop a layout of semi custom ASIC logic cell of three input lookup table (LUT), an FPGA Configurable Logic Block (CLB by using VLSI Digital Schematic Editor & Simulator.